# **Sun4v Hypervisor Core API Specification**

Revision 0.21

March 24, 2005

## **Table of Contents**

| 1 Introduction                      | 3  |

|-------------------------------------|----|

| 1.1 Related specifications          | 3  |

| 1.2 Additional specifications       | 3  |

| 2 Hypervisor call conventions       | 5  |

| 2.1 Hyper-fast traps                | 5  |

| 2.2 Fast traps                      | 5  |

| 2.3 Post hypervisor trap processing | 5  |

| 3 Common definitions                | 7  |

| 3.1 Trap numbers                    | 7  |

| 3.2 Function numbers for FAST_TRAP  | 7  |

| 3.3 Function numbers for CORE_TRAPs | 8  |

| 3.4 Error codes                     | 8  |

| 3.5 Guest states                    | 8  |

| 3.6 Initial guest environment       | 9  |

| 3.7 Privileged registers            | 9  |

| 3.8 Other initial guest state       | 11 |

| 4 Machine description               | 12 |

| 5 API versioning                    | 13 |

| 6 Domain services                   | 14 |

| 6.1 API call                        | 14 |

| 7 CPU services                      | 16 |

| 7.1 CPU id and CPU list             | 16 |

| 7.2 API calls                                    | 16    |

|--------------------------------------------------|-------|

| 8 MMU services                                   | 21    |

| 8.1 Definition for translation table entry (TTH  | E)21  |

| 8.2 Translation Storage Buffer (TSB) specific 21 | ation |

| 8.3 MMU flags                                    | 22    |

| 8.4 MMU Fault status area                        | 23    |

| 8.5 API calls                                    | 26    |

| 9 Cache and Memory services                      | 33    |

| 9.1 API calls                                    | 33    |

| 10 Device interrupt services                     | 35    |

| 10.1 Definitions                                 | 35    |

| 10.2 API calls                                   | 35    |

| 11 Time of day services                          |       |

| 11.1 API calls                                   |       |

| 12 Console services                              | 40    |

| 12.1 API calls                                   | 40    |

| 13 Core dump services                            | 41    |

| 13.1 API calls                                   | 42    |

| 14 Trap trace services                           | 43    |

| 14.1 Trap trace buffer control structure         | 43    |

| 14.2 Trap trace buffer entry format              | 43    |

| 14.3 API calls                                   |       |

|                                                  |       |

## 1 Introduction

This document details the calling conventions of the API provided to a sun4v domain by the underlying hypervisor, and the core functions common to all hypervisors. The intended audience for this document is operating system and firmware engineers porting to the sun4v architecture.

The API serves two principal purposes:

- 1. To enable the supervisor to request services and operations to be performed on its behalf by the hypervisor.

- 2. To inform the hypervisor of information it expects from the supervisor, for example the size and location of the interrupt delivery queues.

## 1.1 Related specifications

This document should be read in conjunction with the following specifications;

The Sun4v Architecture Specification describes the architectural model of the virtual machine environment provided through a conjunction of platform hardware and hypervisor software. It is to be read in addition to the Level-1 SPARC v9 specification. It supplants and extends the Level-2 SPARC v9 specification in describing the programming model, register and exception interfaces for privileged mode software.

The SunSPARC Specification describes the common hardware specification for SPARC processors. It is of primary interest to hypervisor implementors.

The Machine Description Specification documents the transport format and content by which the virtual machine environment implemented by a hypervisor is described to guest software. Many of the arguments provided to hypervisor API services should be derived from or have their constraints (e.g. maximum and minimum values) described by the machine description.

The Sun4v Error Specification documents the behavioral semantics of sun4v virtual machine environment, as well as the syntax of the error reports provided via the resumable and non-resumable error queue interfaces defined by the sun4v architecture.

## 1.2 Additional specifications

Hypervisor API services are divided into three categories; Core, Technology and, Platform Specific.

## 1.2.1 Core API services

Core API services are common to all sun4v virtual machine environments.

## 1.2.2 Technology API services

Technology API services are common to platforms implementing a specific technology requiring a sun4v/hypervisor interface. An example of this category is the PCI IO API specification, which is common to all platforms implementing a virtualized PCI root nexus capability.

## 1.2.3 Platform Specific API services

Platform Specific API services are unique to a platform or platform family only. Examples of such interfaces typically include API services to access performance counters, or processor specific features such as the cryptographic acceleration in Niagara-1.

## 2 Hypervisor call conventions

Hypervisor API calls are made through the use of a trap (Tcc) instruction using  $sw_trap_numbers 0x80$  and above. The calling convention has two forms; fast-trap and hyperfast-trap. The principle difference between these two forms is whether the function number is passed in a register or is encoded in the trap instruction itself. The latter is the faster form, but has a limited number of possible functions, and is therefore reserved for performance critical operations only.

## 2.1 Hyper-fast traps

This trap mechanism encodes the API function number (0x80 + a 7bit value) in the Tcc instruction's *sw\_trap\_number* itself, and therefore provides the fastest possible method of reaching the actual function implementation. The calling convention is as follows:

| Register | Input      | Output        |

|----------|------------|---------------|

| %00      | argument 0 | return status |

| %01      | argument 1 | return value1 |

| %02      | argument 2 | return value2 |

| %03      | argument 3 | return value3 |

| %04      | argument 4 | return value4 |

All arguments and return values are 64-bits unless explicitly stated by the description of a specific API service. Further arguments may be passed in memory, as defined on a per function call basis.

## 2.2 Fast traps

Fast traps are the preferred mechanism for hypervisor API calls. All fast trap API calls use *sw\_trap\_number* 0x80 in the Tcc instruction, with the required function number provided as a 64bit value in register %05. The calling convention is as follows:

| Register | Input                     | Output         |

|----------|---------------------------|----------------|

| %05      | function number           | undefined      |

| %00      | argument 0                | return status  |

| %01      | argument 1                | return value 1 |

| %02      | argument 2 return value 2 |                |

| %03      | argument 3                | return value 3 |

| %04      | argument 4 return value 4 |                |

All arguments and return values are 64-bits unless explicitly stated by the description of a specific API service. Further arguments may be passed in memory, as defined on a per function call basis.

## 2.3 Post hypervisor trap processing

The following convention is used, unless explicitly described for a particular API service:

• All API services resume executing at the next logical instruction after the service trap as with a *done* instruction.

| Α  | <b>Revision 0.21</b> |  |

|----|----------------------|--|

| Ма | rch 24, 2005         |  |

- All sun4v defined registers are preserved across an API service except as explicitly stated below;

- Registers providing arguments to an API service (including the function number %05 for fast traps) should be considered volatile, and their values upon return are undefined unless they are explicitly specified on a per-service basis. Registers not used for passing arguments or returning values are preserved across the API service.

- Upon return from the API service, the returned status is given in register %00. A value of zero in %00 indicates successful execution of the API service, all other values indicate an error status (as defined in section 3.4).

- If an invalid *sw\_trap\_number* is issued, or if an invalid function number is specified, the hypervisor will return with EBADTRAP (as defined in section 3.4) in %00.

- All 64 bits of the argument or return values are significant.

#### **Common definitions** 3

## 3.1 Trap numbers

The following are the sw\_trap\_numbers encoded in the Tcc instruction that enters the hypervisor:

| FAST_TRAP       | 0x80 |

|-----------------|------|

| MMU_MAP_ADDR    | 0x83 |

| MMU_UNMAP_ADDR  | 0x84 |

| TTRACE_ADDENTRY | 0x85 |

| CORE_TRAP       | 0xff |

|                 |      |

Unless assigned to technology or platform specific APIs all other trap numbers (0x86 to 0xfe inclusive) result in EBADTRAP being returned in %00 as described in section 2.3.

### 3.2 Function numbers for FAST\_TRAP

Function numbers for fast-traps are provided in %05 as a 64-bit value. The following are the function numbers defined for the core API set:

| MACH_EXIT                  | 0x00 |

|----------------------------|------|

| MACH_DESC                  | 0x01 |

| MACH_SIR                   | 0x02 |

| CPU_START                  | 0x10 |

| CPU_STOP                   | 0x11 |

| CPU_YIELD                  | 0x12 |

| CPU_QCONF                  | 0x14 |

| CPU_QINFO                  | 0x15 |

| CPU_MYID                   | 0x16 |

| CPU_STATE                  | 0x17 |

| CPU_SET_RTBA               | 0x18 |

| CPU_GET_RTBA               | 0x19 |

| MMU_TSB_CTX0               | 0x20 |

| MMU_TSB_CTXNON0            | 0x21 |

| MMU_DEMAP_PAGE             | 0x22 |

| MMU_DEMAP_CTX              | 0x23 |

| MMU_DEMAP_ALL              | 0x24 |

| MMU_MAP_PERM_ADDR          | 0x25 |

| MMU_FAULT_AREA_CONF        | 0x26 |

| MMU_ENABLE                 | 0x27 |

| MMU_UNMAP_PERM_ADDR        | 0x28 |

| MMU_TSB_CTX0_INF0          | 0x29 |

| MMU_TSB_CTXNON0_INF0       | 0x2a |

| MMU_FAULT_AREA_INF0        | 0x22 |

| MEM_SCRUB                  | 0x31 |

| MEM_SYNC                   | 0x32 |

| CPU_MONDO_SEND             | 0x42 |

| TOD_GET                    | 0x50 |

| TOD_SET                    | 0x51 |

| CONS_GETCHAR               | 0x60 |

| CONS_PUTCHAR               | 0x61 |

| TTRACE_BUF_CONF            | 0x90 |

| TTRACE_BUF_INFO            | 0x91 |

| TTRACE_ENABLE              | 0x92 |

| TTRACE_FREEZE              | 0x93 |

| DUMP_BUF <u>UPDATECONF</u> | 0x94 |

| DUMP_BUF_INFO              | 0x95 |

| 0xa0 |

|------|

| 0xa1 |

| 0xa2 |

| 0xa3 |

| 0xa4 |

| 0xa5 |

| 0xa6 |

|      |

Unless assigned to technology specific or platform specific APIs all other function numbers used for fast-traps result in EBADTRAP being returned in %00 as described in section 2.3.

## 3.3 Function numbers for CORE\_TRAPs

CORE\_TRAP APIs follow the same calling conventions as FAST\_TRAP API services. The following are the function numbers defined for the core API set:

| API_VER     | 0x00 |

|-------------|------|

| API_PUTCHAR | 0x01 |

| API_EXIT    | 0x02 |

CORE\_TRAP function numbers are defined as followed:

API\_VER is defined in section 5.

API\_PUTCHAR is an alias for FAST\_TRAP function CONS\_PUTCHAR.

API\_EXIT is an alias for FAST\_TRAP function MACH\_EXIT.

#### 3.4 Error codes

When a hypervisor API returns, unless explicitly described by the API service, the 64-bit value in %00 will be one of the following error identification values.

| EOK<br>ENOCPU<br>ENORADDR<br>ENOINTR | 0<br>1<br>2<br>3 | Successful return<br>Invalid CPU id<br>Invalid real address<br>Invalid interrupt id |

|--------------------------------------|------------------|-------------------------------------------------------------------------------------|

| EBADPGSZ                             | 4                | Invalid pagesize encoding                                                           |

| EBADTSB                              | 5                | Invalid TSB description                                                             |

| EINVAL                               | 6                | Invalid argument                                                                    |

| EBADTRAP                             | 7                | Invalid function number                                                             |

| EBADALIGN                            | 8                | Invalid address alignment                                                           |

| EWOULDBLOCK                          | 9                | Cannot complete operation without blocking                                          |

| ENOACCESS                            | 10               | No access to specified resource                                                     |

| EIO                                  | 11               | I/O Error                                                                           |

| ECPUERROR                            | 12               | CPU is in error state                                                               |

| ENOTSUPPORTED                        | 13               | Function not supported                                                              |

| ENOMAP                               | 14               | No mapping found                                                                    |

| ETOOMANY                             | 15               | Too many items specified / limit reached                                            |

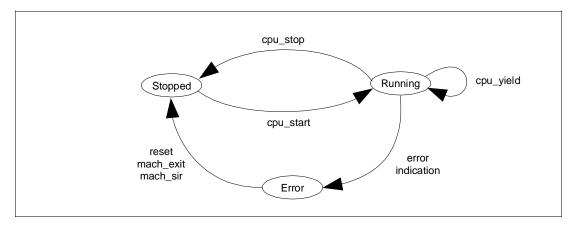

#### 3.5 Guest states

As defined by the Sun4v Architecture Specificiation each virtual CPU can have one of three different states:

| Stopped | CPU is stopped, not executing code, an d may be started via the |

|---------|-----------------------------------------------------------------|

|         | cpu_start API service                                           |

|         |                                                                 |

Running CPU is executing

Error CPU is in error, and no longer executing code

The relationship of these CPU states and hypervisor services may be summarized with

the state diagram below:

## 3.6 Initial guest environment

The initial state of each sun4v virtual CPU is defined in the Sun4v Architecture Specification. Initial register state is duplicated here together with initial register configuration performed by the hypervisor for completeness.

## 3.7 Privileged registers

| Register(s) | Initial Value                             |

|-------------|-------------------------------------------|

| %cwp        | 0                                         |

| %cansave    | NWIN-2                                    |

| %cleanwin   | NWIN-2                                    |

| %canrestore | 0                                         |

| %otherwin   | 0                                         |

| %wstate     | 0                                         |

| %pstate     | all 0 except pstate.priv=1, pstate.mm=tso |

| %tl         | MAXPTL (2)                                |

| %gl         | MAXPGL (2)                                |

| %pil        | MAXPIL (0xf)                              |

| %tba        | current rtba                              |

| %tt         | POR                                       |

## 3.7.1 Non-Privileged Registers

| <u>Register(s)</u>   | Initial Value                          |

|----------------------|----------------------------------------|

| <u>%g1-%g7</u>       | <u>0</u>                               |

| <u>%i0[%cwp]</u>     | real address of startup memory segment |

| <u>%i1[%cwp]</u>     | size of startup memory segment         |

| <u>%i2-%i7[%cwp]</u> | <u>0</u>                               |

| Regis                 | ter(s) Initial Value                        |

|-----------------------|---------------------------------------------|

| <u>%i0-%i7[all ot</u> | <u>ner windows]</u>                         |

| <u>%10-%17[al</u>     | windows] 0                                  |

| <u>%d0-</u>           | <u>8d62</u> <u>Binary 0</u>                 |

| <u>%</u>              | <u>sr</u> <u>0</u>                          |

| Regis                 | t <del>er(s)</del> Initial Value            |

| <mark>%g1</mark>      | <del>%g7</del> <del>0</del>                 |

| <del>%i0[</del> %     | cwp] real address of startup memory segment |

| <del>%i1[</del> %     | cwp] siz cof startup memory segment         |

| <del>%i2 %i7</del>    | l%ewp] 0                                    |

| %i0 %i7[all ot        | her windows] 0                              |

| <del>%d0</del> -      | 6d62 Binary 0                               |

| <del>%</del>          | SF Q                                        |

## 3.7.2 Ancillary State Registers

| Register(s)                    | Initial Value                         |

|--------------------------------|---------------------------------------|

| <u>asr0 (%y)</u>               | <u>0</u>                              |

| <u>asr2 (%ccr)</u>             | <u>0</u>                              |

| <u>asr3 (%asi)</u>             | ASI REAL                              |

| <u>asr4 (%tick)</u>            | <u>&gt;0, npt=0</u>                   |

| <u>asr5 (%pc)</u>              | <u>current pc</u>                     |

| <u>asr6 (%fprs)</u>            | <u>0</u>                              |

| <u>asr19 (%gsr)</u>            | <u>0</u>                              |

| <u>asr22 (%softint)</u>        | <u>0</u>                              |

| asr24 (%stick)                 | <u>&gt;0, npt=0</u>                   |

| <u>asr25 (%stick_cmpr)</u>     | 0 with interrupts disabled (bit 63=1) |

| Register(s)                    | Initial Value                         |

| <del>asr0 (%y)</del>           | θ                                     |

| <del>asr2 (%ccr)-</del>        | θ                                     |

| <del>asr3 (%asi)</del>         | ASI_REAL                              |

| <del>asr4 (%tike</del>         | <del>&gt;0, npt=0</del>               |

| <del>asr5 (%pc)</del>          | <del>current pc</del>                 |

| <del>asr6 (%fprs)</del>        | θ                                     |

| <del>asr10 (%gsr)</del>        | θ                                     |

| <del>asr22 (%softint)</del>    | θ                                     |

| <del>asr24 (%stick)</del>      | <del>&gt;0, npt=0</del>               |

| <del>asr25 (%stick_cmpr)</del> | θ                                     |

## 3.7.3 Internal memory-mapped registers

| Register(s)                              | Initial Value    |

|------------------------------------------|------------------|

| ASI_SCRATCHPAD, VA=0x00                  | 0                |

| ASI_SCRATCHPAD, VA=0x08                  | 0                |

| ASI_SCRATCHPAD, VA=0x10                  | 0                |

| ASI_SCRATCHPAD, VA=0x18                  | 0                |

| ASI_SCRATCHPAD, VA=0x20                  | 0 if implemented |

| ASI_SCRATCHPAD, VA=0x28                  | 0 if implemented |

| ASI_SCRATCHPAD, VA=0x30                  | 0                |

| ASI_SCRATCHPAD, VA=0x38                  | 0                |

| ASI_MMU, VA=0x08 (primary ctx)           | 0                |

| ASI_MMU, VA=0x10 (secondary ctx)         | 0                |

| ASI_MMU, VA= $0xn08$ (for valid {n} > 0) | 0                |

| ASI_MMU, VA= $0xn10$ (for valid {n} > 0) | 0                |

| ASI_QUEUE, VA=0x3c0 (cpu mondo<br>head)  | 0                |

| ASI_QUEUE, VA=0x3c8 (cpu mondo tail)     | 0                |

| ASI_QUEUE, VA=0x3d0 (dev mondo<br>head)  | 0                |

| ASI_QUEUE, VA=0x3d8 (dev mondo tail)     | 0                |

| ASI_QUEUE, VA=0x3e0 (res. error head)    | 0                |

| ASI_QUEUE, VA=0x3e8 (res. error tail)    | 0                |

| ASI_QUEUE, VA=0x3f0 (nres. error head)   | 0                |

| ASI_QUEUE, VA=0x3f8 (nres. error tail)   | 0                |

## 3.7.4 CPU-specific Registers

Platform specific performance counters will be configured such that exceptions/interrupts are disabled.

## 3.8 Other initial guest state

MMU state is disabled.

MMU fault status area location is undefined.

TSB info is undefined.

All queue base addresses and sizes are undefined.

One CPU is placed into the running state, all other CPUs are in the stopped state.

## 4 Machine description

To describe the resources within a virtual machine (or logical domain), a data structure called a machine description is made available to a guest operating system. The machine description content and its binary format is currently described in a separate document - to be combined with this.

## 5 API versioning

This section describes the API versioning interface available to all privileged code. *This API interface is to be defined.*

## 6 Domain services

The following services enable privileged software to request information about or to affect the entire virtual machine domain.

## 6.1 API call

#### 6.1.1 mach\_exit

| trap#     | FAST_TRAP |

|-----------|-----------|

| function# | MACH_EXIT |

| arg0      | exit_code |

This service stops all CPUs in the virtual machine domain and places them into the *stopped* state. The 64-bit *exit\_code* may be passed to a service entity as the domain's exit status.

On systems without a service entity, the domain will undergo a reset, and the boot firmware will be reloaded.

This function will never return to the guest that invokes it.

Note: by convention a exit\_code of zero denotes successful exit by the guest code. A non-zero exit\_code denotes a guest specific error indication.

#### 6.1.1.1 Errors

This service does not return.

#### 6.1.2 mach\_desc

| trap#     | FAST_TRAP |

|-----------|-----------|

| function# | MACH_DESC |

| arg0      | buffer    |

| arg1      | length    |

| ret0      | status    |

| ret1      | length    |

This service copies the most current machine description into the buffer indicated by the real address in arg0. The buffer provided must be 16 byte aligned. <u>Upon success or EINVAL</u> <u>this service returns</u>, and a minimum of 64bytes in size. In all cases upon return the actual size of the machine description is provided in the ret1 (length) return value.

Note: A method of determining the appropriate buffer size for the machine description is to first call this service with a buffer length of 0 bytes. The service will always return the machine description size in ret1.

#### 6.1.2.1 Errors

| EBADALIGN | Buffer is badly aligned                         |

|-----------|-------------------------------------------------|

| ENORADDR  | Buffer is to an illegal real address.           |

| EINVAL    | Buffer length is too small for complete machine |

|           | description.                                    |

## 6.1.3 mach\_sir

trap# function# FAST\_TRAP MACH\_SIR

This service provides a software initiated reset of a virtual machine domain. All CPUs are <u>captured as soon as possible</u>, all hardware devices are returned to the entry default state, and the domain is restarted at the SIR (trap type 0x4) real trap table (rtba) entry point on one of the CPUs. The single CPU restarted is selected as determined by platform specific policyimmediately captured, all hardware devices are returned to the entry default state, and the domain is restarted at the SIR (trap type 0x4) real trap table (rtba) entry point on one of the cPUs. Memory is preserved across this operation.

### 6.1.3.1 Errors

This service does not return.

## 7 CPU services

CPUs represent devices that can execute software threads. A single chip that contains multiple cores or strands is represented as multiple CPUs with unique CPU identifiers. CPUs are exported to OBP via the machine description (and to Solaris via the device tree). CPUs are always in one of three states: *stopped*, *runningstarted*, or *error*.

## 7.1 CPU id and CPU list

<u>A cpu id is a pre-assigned 16bit value that uniquely identifies a CPU within a logical</u> <u>domain</u>Operations that are to be be performed on multiple CPUs specify them via a CPU list. A CPU list is an array of 16 bit words in real memory, each of which is a CPU id.

Operations that are to be be performed on multiple CPUs specify them via a CPU list. A CPU list is an array in real memory, of which each 16-bit word is a CPU id CPU lists are passed through the API as 2 arguments: the first is the number of entries (16 bit words) in the CPU list, and the second is the (real address) pointer to the CPU id list.

<u>CPU lists are passed through the API as two arguments: the first is the number of entries</u> (16-bit words) in the CPU list, and the second is the (real address) pointer to the CPU id list.

## 7.2 API calls

## 7.2.1 cpu\_start

| trap#<br>function# | FAST_TRAP<br>CPU START |

|--------------------|------------------------|

| arg0               | cpuid                  |

| argl               | pc                     |

| arg2               | rtba                   |

| arg3               | <pre>target_arg0</pre> |

|                    |                        |

ret0

status

Start CPU with id *cpuid* with *pc* in %pc and with a real trap base address value of *rtba*. The indicated CPU must be in the *stopped* state. The supplied rtba must be aligned on a 256byte boundary. On successful completion, the specified cpu will be in the *running* state and On successful completion, it will be in the *started* state. The target CPU will be supplied with *target\_arg0* in %o0 and *rtba* in %tba.

## 7.2.1.1 Errors

| ENOCPU      | Invalid <i>cpuid</i>                            |

|-------------|-------------------------------------------------|

| EINVAL      | Target <i>cpuid</i> is not in the stopped state |

| ENORADDR    | Invalid <i>pc</i> or <i>rtba</i> real address   |

| EBADALIGN   | <u>Unaligned pc or unaligned rtba</u>           |

| EWOULDBLOCK | <u>if starting resource is not available</u>    |

### 7.2.2 cpu\_stop

| trap#     | FAST_TRAP |

|-----------|-----------|

| function# | CPU_STOP  |

| arg0      | Cpu       |

| ret0      | status    |

Stop CPU *cpu*. The indicated CPU must be in the *running* state. On completion, it will be in the *stopped* state. It is not legal to stop the current CPU.

<u>Note:</u> As this service cannot be used to stop the current cpu, this service may not be used to stop the last running CPU in a domain. To stop and exit a running domain a Programming note: As this service cannot be used to stop the current cpu, this service may not be used to stop the last running CPU in a domain. To stop and exit a running domain the guest must use the mach\_exit service.

### 7.2.2.1 Errors

| ENOCPU        | Invalid <i>cpu</i>                           |

|---------------|----------------------------------------------|

| EINVAL        | target <i>cpu</i> is the current cpu         |

| EINVAL        | target cpu is not in the running state       |

| EWOULDBLOCK   | <u>if stopping resource is not available</u> |

| ENOTSUPPORTED | if not supported on the platform             |

|               |                                              |

#### 7.2.3 cpu\_set\_rtba

| trap#     | FAST_TRAP     |

|-----------|---------------|

| function# | CPU_SET_RTBA  |

| arg0      | rtba          |

| ret0      | status        |

| ret1      | previous_rtba |

Set the real trap base address of the local cpu to the value of r*tba*. <u>The supplied rtba must</u> <u>be aligned on a 256byte boundary</u>. Upon success the previous value of rtba is returned in ret1.

Note: the real trap table is described in the sun4v architecture specification.

Note: this service does not affect %tba

Programming note: this service does not affect %tba

#### 7.2.3.1 Errors

ENORADDR EBADALIGN Invalid *rtba* real address rtba is incorrectly aligned for a trap table

#### 7.2.4 cpu\_get\_rtba

trap# function# FAST\_TRAP CPU\_GET\_RTBA

ret0 ret1 status previous\_rtba

Returns the current value of rtba in ret1.

7.2.4.1 <u>Errors</u>

No possible error

## 7.2.5 cpu\_yield

| trap#     | FAST_TRAP |

|-----------|-----------|

| function# | CPU YIELD |

|           | —         |

| ret0      | status    |

Suspend execution on the current CPU. Execution will resume when a interrupt (device, stick\_cmpr, or cross-call) is targeted to the CPU. On some CPUs, this API may be used by the hypervisor to save power by disabling hardware strands.

#### 7.2.5.1 Errors

No possible error

#### 7.2.6 cpu\_qconf

| trap#     | FAST_TRAP  |

|-----------|------------|

| function# | CPU_QCONF  |

| arg0      | queue      |

| arg1      | base raddr |

| arg2      | nentries   |

| ret0      | status     |

Configure queue *queue* to be placed at real address *base*, and of *nentries* entries. nentries must be a power of two number of entries. B*ase* must be aligned exactly to match the queue size. Each queue entry is 64 bytes long, so for example, a 32 entry queue must be aligned on a 2048 byte real address boundary.

The specified queue is un-configured if nentries is 0.

For the current version of this API service the argument queue is defined as follows:

| queue | description               |

|-------|---------------------------|

| 0x3c  | cpu mondo queue           |

| 0x3d  | device mondo queue        |

| 0x3e  | resumable error queue     |

| 0x3f  | non-resumable error queue |

Programming note: The maximum number of entries for each queue for a specific cpu may be determined from the machine description.

## 7.2.6.1 Errors

| ENORADDR  | Invalid <i>base</i>                              |

|-----------|--------------------------------------------------|

| EINVAL    | Invalid <i>queue</i> or,                         |

|           | <i>nentries</i> not a power of two in number or, |

|           | nentries is less than two or too large.          |

| EBADALIGN | baseaddr is not correctly aligned for size       |

#### 7.2.7 cpu\_qinfo

| trap#     | FAST_TRAP  |

|-----------|------------|

| function# | CPU_QINFO  |

| arg0      | queue      |

| ret0      | status     |

| ret1      | base raddr |

| ret2      | nentries   |

Return the configuration info for queue *queue*. The base\_raddr is the currently defined read address base of the defined queue, and nentries is the size of the queue in terms of number of entries.

For the current version of this API service the argument queue is defined as follows:

| queue | description               |

|-------|---------------------------|

| 0x3c  | cpu mondo queue           |

| 0x3d  | device mondo queue        |

| 0x3e  | resumable error queue     |

| 0x3f  | non-resumable error queue |

If the specified queue is a valid queue number, but no queue has been defined this service will return success, but with nentries set to 0 and base\_raddr will have an undefined value.

#### 7.2.7.1 Errors

EINVAL Invalid queue

#### 7.2.8 cpu\_mondo\_send

| trap#     | FAST_TRAP      |

|-----------|----------------|

| function# | CPU_MONDO_SEND |

| arg0-1    | cpulist        |

| arg2      | data           |

| ret0      | status         |

Send a mondo interrupt to CPU list *cpulist* with 64 bytes of data pointed to by *data. data* must be a 64 byte aligned real address. The mondo data will be delivered to the cpu\_mondo queues of the recipient cpus.

In <u>all cases, (error or no), the</u><u>the event of a detected error</u>, cpus in *cpulist* to which the mondo has been successfully delivered will be indicated by having their entry in *cpulist* updated with the value 0xffff.

#### 7.2.8.1 Errors

| EBADALIGN   | Mondo data is not 64byte aligned                                                 |

|-------------|----------------------------------------------------------------------------------|

| ENORADDR    | or cpulist is not 2byte aligned<br>Invalid <i>data</i> mondo address <u>, or</u> |

|             | <u>invalid cpu list address</u>                                                  |

| ENOCPU      | Invalid CPU in cpus                                                              |

| EWOULDBLOCK | Some or all of the listed cpus did not                                           |

|             | receive the mondo                                                                |

| EINVAL      | cpulist includes caller's cpuid                                                  |

| trap#     | FAST_TRAP |

|-----------|-----------|

| function# | CPU_MYID  |

| ret0      | status    |

| ret1      | cpuid     |

Return the hypervisor ID handle for the current CPU. Used by a virtual cpu to discover its own identity.

## 7.2.9.1 <u>Errors</u>

#### No errors defined

## 7.2.10 cpu\_state

| trap#     | FAST_TRAP |

|-----------|-----------|

| function# | CPU_STATE |

| arg0      | cpuid     |

| ret0      | status    |

| ret1      | state     |

Retrieve the current state of cpu cpuid. Therunning state of cpu cpuid. The running states

are:

| 0x1 | <u>cpu</u> | is              | in                | the                  | stopped                  | <u>state</u> IDLE         | <del>0x1</del>                                  | - <del>cpu</del>                                                                                                                                                     |

|-----|------------|-----------------|-------------------|----------------------|--------------------------|---------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |            |                 |                   |                      |                          |                           |                                                 |                                                                                                                                                                      |

| 0x2 | <u>cpu</u> | is              | in                | the                  | running                  | <u>stat</u> GUEST         | <del>0x2</del>                                  | - <del>cpu</del>                                                                                                                                                     |

|     |            |                 |                   |                      |                          |                           |                                                 |                                                                                                                                                                      |

| 0x3 | cpu        | is              | in                | the                  | error st                 | tate                      |                                                 |                                                                                                                                                                      |

| (   | )x2        | ) <u>x2 cpu</u> | )x2 <u>cpu is</u> | )x2 <u>cpu is in</u> | )x2 <u>cpu is in the</u> | )x2 cpu is in the running | )x2 cpu is in the running stat <del>GUEST</del> | Dx1 <u>cpu is in the stopped state</u> <del>IDLE</del> <del>0x1<br/>Dx2 <u>cpu is in the running stat</u>GUEST</del> <del>0x2</del><br>Dx3 cpu is in the error state |

## 7.2.10.1 Errors

ENOCPU

Invalid CPU in cpuid

## 8 MMU services

These hypervisor services control the behavior of address translations handled by the hypervisor.

A basic sun4v guest operating system, need not use any of these services at all. The default/initial operating environment for a guest is with virtual address translation disabled. In this mode all instructions and data references are made with real addresses.

If a guest operating system enables MMU translations, then virtual to real mappings may be specified in one of three different ways; either as permanent mappings, or as mappings that may be evicted and reloaded into system TLBs directly via MMU service functions, or indirectly via Translation Storage Buffers (TSBs). Moreover, with translations enabled, a guest Operating System must declare a Fault Status area for the hypervisor to provide information in the event of a translation fault.

## 8.1 Definition for translation table entry (TTE)

The format of a translation table entry (TTE) is defined in the Sun4v Architecture Specification.

## 8.2 Translation Storage Buffer (TSB) specification

The TSB functions control two sets of TSBs, one for when the virtual address context is zero, and one for when it is not zero. The demap functions remove translations from hardware TLBs. See the Address Model chapter in the sun4v Architecture Specification for more information on TSBs and TLBs.

A TSB description is a memory data structure that defines a single TSB:

| offset<br>0<br>2<br>4<br>8<br>12<br>16 | size<br>2<br>4<br>4<br>4<br>8 | contents<br>page size to use for index shift in TSB<br>associativity of TSB<br>size of TSB in TTEs (16 bytes)<br>context <u>index</u><br>page size bitmask<br>real address of TSB base |

|----------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24                                     | 8                             | reserved                                                                                                                                                                               |

The maximum TSB associativity supported is indicated in the machine description. An associativity value of 0xffff is reserved and should not be used for version 1.0 of this specification.

#### 8.2.1 Page sizes

The Sun4v Architecture Specification defines value encodings of page size for translation table entries (TTEs). The page size bitmask indicates which of these encodings may be specified for TTEs within a given TSB. For each bit in the page size bitmask, if set, the sun4v page size may be specified. For example, bit 0 corresponds to an 8KByte page size, bit 1 to a 64K page size, and so on in multiples of 8 of the page size for each bit in the field:

| Bit | Page size |

|-----|-----------|

| 0   | 8K        |

| 1   | 64K       |

| 2   | 512K      |

| 3   | 4MB       |

| 4   | 32MB      |

| 5   | 256MB     |

| б   | 2GB       |

|     |           |

7

16GB

Bits 8 through 15 are reserved and must be set to zero.

The index shift page size indicates the page size to use for computing the TSB index for TTE retrieval. This value is the same as the page size value that may be specified in an individual sun4v TTE:

| Value | Page size assumed for index computation |

|-------|-----------------------------------------|

| 0     | 8K                                      |

| 1     | 64K                                     |

| 2     | 512K                                    |

| 3     | 4MB                                     |

| 4     | 32MB                                    |

| 5     | 256MB                                   |

| б     | 2GB                                     |

| 7     | 16GB                                    |

Values 8 though 15 are reserved. The index shift value must correspond to the smallest page size specified in the page size bit mask.

## 8.2.2 Context index

This <u>TSB</u> description field enables <u>TSBs</u> to be defined where the context value for a pagetranslation is supplied within each entry of the <u>TSB</u>, or where a single value applies to the whole <u>TSB</u>. The latter enables a single <u>TSB</u> to be used for multiple context values (the context field within each <u>TSB</u> entry (<u>TTE</u>) is required to be zero). The context index field within a TSB description selects which of these two modes the <u>TSB</u> is defined to use.

If a context index field value of -1 (0xfffffff) is given in the TSB description, the TSB is defined to use the context field within each TTE.

If a context index field contains a value between 0 and mmu-#shared-contexts, the context value used for every entry in the TSB (TTE) will be taken from sun4v context register identified by the context index field at the time the TTE is used. For example for a translation required for (express or implied) ASI PRIMARY and matched by a TTE in the TSB, will take its context value from the register PRIMARY CONTEXT1 if the context index field of the TSB description is 1.

Any other value supplied in context index field is invalid.

The value of mmu-#shared-contexts is provided in the "cpu" node of description enables TSBs to be defined where the context value for a page translation is supplied within each entry of the TSB, or where a single value applies to the whole TSB. The latter enables a single TSB to be used for multiple context values (the context field within each TSB entry is required to be zero). The context field within the description selects which of these two modes the TSB is defined to use. If context contains a value between 1 and max\_context that is the context value applied to every entry in the TSB. If a context value of 1 is given in the TSB description, then the TSB is defined to use the context field within each TTE. Any other value supplied in context will return an EINVAL error. max\_context is provided by the machine description for each virtual cpu.

#### 8.3 MMU flags

The MMU APIs are designed to function for both instruction and data address

translations. Therefore, many of these interfaces take an MMU 'flags' argument in order to specify whether the operation is relevant to instruction or data mappings, or both. To ensure consistency between the MMU services this flags argument is defined here, and as follows:

The flags argument applies the API operation to instruction translations if bit 1 is set, and in addition applies the API operation to data translation entries if bit 0 is set. For every API service requiring a flags argument, at least one of bit 0 and/or bit 1 must be set.

**Implementation note:** For hardware implementations with unified instruction and data functions (for example; TLBs); Mapping an instruction translation entry may also cause an identical data translation entry to be mapped, and vice-versa even if not explicitly requests by the flags argument. Similarly, demapping an instruction translation entry may also cause the data translation entry to be demaped, and vice-versa even if not explicitly requests by the flags.

## 8.4 MMU Fault status area

MMU related faults have their status and fault address information placed into a memory region made available by privileged code. Like the TSBs above, the fault status area for **each** virtual processor is declared to the hypervisor via a hypervisor API call.

It is possible for MMU related faults to be delivered either by the hypervisor or directly by processor hardware if so implemented. For this reason, the MMU fault area is arranged on an aligned address boundary with instruction and data fault fields arranged into distinct 64byte blocks.

| Offset (bytes) | <u>Size (bytes)</u> | <u>Field</u>                     |

|----------------|---------------------|----------------------------------|

| <u>0x00</u>    | <u>0x8</u>          | Instruction fault type (IFT)     |

| <u>0x08</u>    | <u>0x8</u>          | Instruction fault address (IFA)  |

| <u>0x10</u>    | <u>0x8</u>          | Instruction fault context A(IFC) |

| <u>0x18</u>    | <u>0x28</u>         | reserved                         |

| <u>0x40</u>    | <u>0x8</u>          | Data fault type (DFT)            |

| <u>0x48</u>    | <u>0x8</u>          | Data fault address (DFA)         |

| <u>0x50</u>    | <u>0x8</u>          | Data fault context (DFC)         |

| <u>0x58</u>    | <u>0x28</u>         | reserved                         |

The layout of the MMU fault status area is described in the table below:

<u>The reserved fields must not be used. Their contents are undefined, and are not guaranteed preserved if written.</u>

| Offset (bytes)  | <del>Size (bytes)</del> | Field                               |

|-----------------|-------------------------|-------------------------------------|

| <del>0x00</del> | 8                       | Instruction fault type (IFT)        |

| <del>0x08</del> | 8                       | Instruction fault address (IFA)     |

| <del>0x10</del> | 8                       | Instruction fault context A(IFC)    |

| <del>0x40</del> | 8                       | <del>Data fault type (DFT)</del>    |

| <del>0x48</del> | 8                       | <del>Data fault address (DFA)</del> |

| <del>0x50</del> | 8                       | <del>Data fault context (DFC)</del> |

The definition of the values of the instruction and data fault type fields is as follows:

| Code                   | Fault type              |  |

|------------------------|-------------------------|--|

| 1                      | fast miss               |  |

| 2                      | fast protection         |  |

| 3                      | MMU miss                |  |

| 4                      | invalid RA              |  |

| 5                      | privileged violation    |  |

| 6                      | protection violation    |  |

| 7                      | NFO access              |  |

| 8                      | so page/NFO side effect |  |

| 9                      | invalid VA              |  |

| 10                     | invalid ASI             |  |

| 11                     | nc atomic               |  |

| 12                     | privileged action       |  |

| 13                     | reserved                |  |

| 14                     | unaligned access        |  |

| 15                     | invalid page size       |  |

| 16 to -2               | reserved                |  |

| -1 (0xffffffffffffffff | multiple errors         |  |

For each MMU related trap, the fault status area is updated as follows; (a blank entry for IFT,IFA,IFC,DFT,DFA or DFC indicates the field is not updated for the particular condition and is therefore undefined, and '•' indicates the field is updated with the relevant fault type, address or context information for the trap).

| sun4v trap type              | Fault type                 | IFT | IFA | IFC | DFT | DFA | DFC | Comments                                                                 |

|------------------------------|----------------------------|-----|-----|-----|-----|-----|-----|--------------------------------------------------------------------------|

| instruction_access_exception | invalid RA (0x4)           | •   | •   |     |     |     |     | instruction fetch to real address out of range                           |

|                              | privilege violation (0x5)  | •   | •   | •   |     |     |     | non privileged<br>instruction access to<br>privileged page<br>(TTE.p=1)  |

|                              | NFO access (0x7)           | •   | •   | •   |     |     |     | instruction access to<br>non-faulting load page<br>(TTE.nfo=1)           |

|                              | invalid VA (0x9)           | •   | •   | •   |     |     |     | instruction virtual access out of range                                  |

|                              | Invalid TSB entry          | •   | •   | •   |     |     |     | Hardware table walk<br>found an invalid RA in a<br>TTE loaded from a TSB |

|                              | Protection violation (0x6) | •   | •   | •   |     |     |     | Instruction access to<br>page without execute<br>permission              |

|                              | Multiple error (-1)        | •   |     |     |     |     |     | Hardware encountered<br>multiple errors                                  |

| instruction_access_MMU_miss  | MMU miss (0x3)             | •   | ٠   | •   |     |     |     | TSB Miss                                                                 |

| sun4v trap type                                              | Fault type                       | IFT | IFA | IFC | DFT | DFA | DFC | Comments                                                                                           |

|--------------------------------------------------------------|----------------------------------|-----|-----|-----|-----|-----|-----|----------------------------------------------------------------------------------------------------|

| data_access_exception                                        | invalid RA (0x4)                 |     |     |     | •   | •   | •   | real address out of range                                                                          |

|                                                              | privilege violation (0x5)        |     |     |     | •   | •   | •   | Non-privileged data<br>access to privileged<br>page (TTE.p=1)                                      |

|                                                              | NFO access (0x7)                 |     |     |     | •   | •   | •   | Data access to non-<br>faulting page<br>(TTE.nfo=1) with ASI<br>other than a non-<br>faulting ASI. |

|                                                              | so page/NFO side effect<br>(0x8) |     |     |     | •   | •   | •   | Non-faulting ASI data<br>access to side-effect<br>page (TTE.e=1)                                   |

|                                                              | invalid VA (0x9)                 |     |     |     | •   | •   | •   | Data or branch virtual<br>access out of range                                                      |

|                                                              | invalid ASI (0xa)                |     |     |     | •   | •   | •   | Invalid ASI for<br>instruction                                                                     |

|                                                              | nc atomic (0xb)                  |     |     |     | •   | •   | •   | Atomic access to non-<br>cacheable page<br>(TTE.cp=0)                                              |

|                                                              | privileged action (0xc)          |     |     |     | •   | •   | •   | Data access by non-<br>privileged software<br>using a privileged or<br>hyper-privileged ASI        |

|                                                              | invalid page size (0xf)          |     |     |     | •   |     |     |                                                                                                    |

|                                                              | Multiple error (-1)              |     |     |     | •   |     |     | Hardware encountered<br>multiple errors                                                            |

| data_access_MMU_miss                                         | MMU miss (0x3)                   |     |     |     | •   | •   | •   | TSB Miss                                                                                           |

| data_access_protection                                       | protection violation (0x6)       |     |     |     | •   | •   | •   | store to non-writeable ??                                                                          |

| mem_address_not_aligned                                      |                                  |     |     |     |     | •   | •   | -                                                                                                  |

| LDDF_mem_address_not_aligned<br>STDF_mem_address_not_aligned | unaligned access (0xe)           |     |     |     |     | •   | •   | Data access is not<br>properly aligned                                                             |

| LDQF_mem_address_not_aligned<br>STQF_mem_address_not_aligned |                                  |     |     |     |     | •   | •   |                                                                                                    |

| fast_instruction_access_MMU_miss                             | fast miss (0x1)                  |     | •   | •   |     |     |     | TLB Miss                                                                                           |

| fast_data_access_MMU_miss                                    | fast miss (0x1)                  |     |     |     |     | •   | •   | TLB MIss                                                                                           |

| fast_data_access_protection                                  | fast protection (0x2)            |     |     |     |     | •   | •   | Store data access to page<br>without write<br>permission                                           |

| privileged_action                                            | privileged action (0xc)          |     |     |     |     | •   | •   | Use of privileged ASI<br>when pstate.priv = 0                                                      |

## 8.5 API calls

### 8.5.1 mmu\_tsb\_ctx0

trap# function# arg0 arg1

ret0

ntsb tsbdptr status

FAST\_TRAP

MMU\_TSB\_CTX0

Configures the TSBs for the current CPU for virtual addresses with context zero. *tsbdptr* is a pointer to an array of *ntsbs* TSB descriptions.

<u>Note: the maximum number of TSBs available to a virtual CPU is given by the mmu-</u> <u>max-#tsbs property of the cpu's corresponding "cpu" node in the machine description</u> <del>maximum of 16 TSBs maybe specified in the TSB description list</del>.

#### 8.5.1.1 Errors

| ENORADDR<br>EBADALIGN     | Invalid <u>tsbdptr or </u> TSB base in a TSB descriptor<br><u>tsbdptr is not aligned to an 8 byte boundary, or</u> |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|

|                           | <u>TSB base in a descriptor is not aligned for a</u>                                                               |

|                           | <u>TSB size</u>                                                                                                    |

| EBADPGSZ                  | Invalid pagesize in a TSB descriptor                                                                               |

| EBADTSB                   | Invalid associativity or size in a TSB descriptor                                                                  |

| EINVAL                    | Invalid <i>ntsbs</i> , or                                                                                          |

|                           | <u>invalid context index in a TSB descriptor, <del>non -</del></u>                                                 |

| <del>zero context i</del> | <del>in a TSB descript</del> or                                                                                    |

|                           | <u>index page size not equal to smallest page size</u>                                                             |

|                           | <u>in page size bitmask field.</u>                                                                                 |

#### 8.5.2 mmu\_tsb\_ctxnon0

| trap#     | FAST_TRAP       |

|-----------|-----------------|

| function# | MMU_TSB_CTXNON0 |

| arg0      | ntsb            |

| arg1      | tsbdptr         |

| ret0      | status          |

Configures the TSBs for the current CPU for virtual addresses with non-zero contexts. *tsbdptr* is a pointer to an array of *ntsbs* TSB descriptions.

A maximum of 16 TSBs may be specified in the TSB description list.

### 8.5.2.1 Errors

| ENORADDR        | Invalid <u>tsbdptr or </u> TSB base in a TSB descriptor           |

|-----------------|-------------------------------------------------------------------|

| EBADALIGN       | tsbdptr is not aligned to an 8 byte boundary, or                  |

|                 | <u>TSB base in a descriptor is not aligned for a</u>              |

|                 | T <u>SB size</u>                                                  |

| EBADPGSZ        | Invalid pagesize in a TSB descriptor                              |

| EBADTSB         | Invalid associativity or size in a TSB descriptor                 |

| EINVAL          | Invalid <i>ntsbs</i> , or                                         |

|                 | <u>invalid context index in a TSB descriptor, <del>zero</del></u> |

| context in a Ta | <del>SB descript</del> or                                         |

|                 | <u>index page size not equal to smallest page size</u>            |

|                 | in page size bitmask field.                                       |

|                 |                                                                   |

#### 8.5.3 mmu\_demap\_page

| trap#<br>function#<br>arg0<br>arg1<br>arg2<br>arg3<br>arg4 | FAST_TRAP<br>MMU_DEMAP_PAGE<br><i>reserved</i><br>vaddr<br>context<br>flags |

|------------------------------------------------------------|-----------------------------------------------------------------------------|

|                                                            |                                                                             |

ret0

status

Demaps any page mapping of virtual address *vaddr* in context *context* for the current virtual CPU. Any virtual tagged caches are guaranteed to be kept consistent. The flags argument is defined according to section 8.3; "MMU flags".

Arguments arg0 and arg1 are reserved and must be set zero.

#### 8.5.3.1 Errors

The implementation of this function is not required to check for all possible errors, and may return the following error codes:

EINVAL Invalid vaddr, context or flag value ENOTSUPPORED arg0 or arg1 is non-zero

#### 8.5.4 mmu\_demap\_ctx

| trap#<br>function#<br>arg0<br>arg1<br>arg2<br>arg3 | FAST_TRAP<br>MMU_DEMAP_CTX<br><i>reserved</i><br>context<br>flags |

|----------------------------------------------------|-------------------------------------------------------------------|

| ret0                                               | status                                                            |

Demaps all <u>non-permanent virtual page mappings previously specified for context</u> <u>context for the current virtual CPU.mappings for context context for the current virtual CPU</u> Any virtual tagged caches are guaranteed to be kept consistent. The flags argument is defined according to section 8.3; "MMU flags".

Arguments arg0 and arg1 are reserved and must be set zero.

### 8.5.4.1 Errors

The implementation of this function is not required to check for all possible errors, and may return the following error codes:

EINVAL Invalid context or flag value ENOTSUPPORED arg0 or arg1 is non-zero

| trap#     | FAST_TRAP     |

|-----------|---------------|

| function# | MMU_DEMAP_ALL |

| arg0      | reserved      |

| arg1      | reserved      |

| arg2      | flags         |

| ret0      | status        |

Demaps all <u>non-permanent virtual page mappings previously specified</u>translations for the current virtual CPU. Any virtual tagged caches are guaranteed to be kept consistent. The flags argument is defined according to section 8.3; "MMU flags".

Arguments arg0 and arg1 are reserved and must be set zero.

8.5.5.1 Errors

The implementation of this function is not required to check for all possible errors, and may return the following error codes:

| EINVAL       | Invalid | flag | value       |

|--------------|---------|------|-------------|

| ENOTSUPPORED | arg0 or | argl | is non-zero |

#### 8.5.6 mmu\_map\_addr

| trap#<br>arg0<br>arg1<br>arg2 | MMU_MAP_ADDR<br>vaddr<br>context<br>TTE |

|-------------------------------|-----------------------------------------|

| arg2<br>arg3                  | flags                                   |

| ret0                          | status                                  |

This API service creates a non-permanent mapping using the TTE to virtual address *vaddr* for *context* for the calling virtual CPU. The flags argument is defined according to section 8.3; "MMU flags".

Given a TTE specified with the valid bit clear, this service will have undefined behavior.

<u>Note: This API call is for privileged code to specify temporary translation mappings without the</u> <u>need to create and manage a TSB.</u>

Note: This API call is intended both for privileged code that does not use TSBs, and for privileged code to specify temporary translation mappings.

#### 8.5.6.1 Errors

The implementation of this function is not required to check for all possible errors, and may return the following error codes:

| EINVAL                             | Invalid | vaddı | c, cor | ntex | ct, | or  | flag | error |

|------------------------------------|---------|-------|--------|------|-----|-----|------|-------|

| EBADPGS <mark>Z<del>I</del></mark> | Invalid | page  | size   | val  | ue  |     |      |       |

| ENORADDR                           | Invalid | real  | addre  | ess  | in  | TTE | 2    |       |

#### 8.5.7 mmu\_map\_perm\_addr

| trap#     | FAST_TRAP              |

|-----------|------------------------|

| function# | MMU_MAP_PERM_ADDR      |

| arg0      | vaddr                  |

| arg1      | <u>reservedcontext</u> |

| arg2      | TTE                    |

| arg3      | flags                  |

| ret0      | status                 |

This API service creates a permanent mapping using the TTE to virtual address *vaddr* for the calling virtual CPU for context 0. The *reserved* field must be specified as zero*context* for the calling virtual CPU.

A maximum of 8 such permanent mappings may be specified by privileged code. Mappings may be removed with **mmu\_unmap\_perm\_addr** below.

The flags argument is defined according to section 8.3; "MMU flags".

<u>Given a TTE specified with the valid bit clear, this service will have undefined</u> <u>behavior</u>. *Note: This API call used used to specify address space mappings for which privileged code does not expect to receive misses. For example, this mechanism can be used to map kernel nucleus code and data*.

<u>Note: This API call is used to specify address space mappings for which privileged code does not</u> <u>expect to receive misses. For example, this mechanism can be used to map kernel nucleus code and</u> <u>data.</u>

8.5.7.1 Errors

| EINVAL                              |

|-------------------------------------|

| EBADPGS <mark>Z</mark> <del>I</del> |

| ENORADDR                            |

| ETOOMANY                            |

Invalid vaddr, <del>context,</del>or flag error Invalid page size value Invalid real address in TTE Too many mappings (maximum of 8 reached)

#### 8.5.8 mmu\_unmap\_addr

| trap# | MMU_UNMAP_ADDR |

|-------|----------------|

| arg0  | vaddr          |

| arg1  | context        |

| arg2  | flags          |

| ret0  | status         |

Demaps virtual address *vaddr* in context *context* on this CPU. This function is intended to be used to demap pages mapped with **mmu\_map\_addr**. This service is equivalent to invoking **mmu\_demap\_page** with only the current CPU in the CPU list.

The flags argument is defined according to section 8.3; "MMU flags".

Attempting to perform an unmap operation for a previously defined permanent mapping will have undefined results.

#### 8.5.8.1 Errors

The implementation of this function is not required to check for all possible errors, and may return the following error codes:

EINVAL

Invalid vaddr, context or flag value

#### 8.5.9 mmu\_unmap\_perm\_addr

| trap#     | FAST_TRAP               |

|-----------|-------------------------|

| function# | MMU_UNMAP_PERM_ADDR     |

| arg0      | vaddr                   |

| arg1      | <u>reserved</u> context |

| arg2      | flags                   |

| ret0      | status                  |

Demaps any permanent page mapping (established via mmu\_map\_perm\_addr) of virtual address *vaddr* for context <u>Oin context context</u> for the current virtual CPU. Any virtual tagged caches are guaranteed to be kept consistent.

The flags argument is defined according to section 8.3; "MMU flags".

8.5.9.1 Errors

| EINVAL | Invalid vaddr <del>, context</del> or flag value |

|--------|--------------------------------------------------|

| ENOMAP | Specified mapping was not found                  |

## 8.5.10 mmu fault area conf

#### 8.5.11 mmu\_fault\_area

| trap#<br>function#<br>arg0 | FAST_TRAP<br>MMU_FAULT_AREA <u>CONF</u><br>raddr |

|----------------------------|--------------------------------------------------|

| ret0<br>ret1               | status<br>previous mmu fault area raddr          |

Configure the MMU fault status area for the calling CPU. A 64 byte aligned real address specifies where MMU fault status information is placed. The return value is the previously specified area, or 0 for the first invocation. Specifying a fault area at real address 0 is not allowed.

#### 8.5.11.1 Errors

| ENORADDR  | Invalid | real addre | ess |       |      |

|-----------|---------|------------|-----|-------|------|

| EBADALIGN | Invalid | alignment  | for | fault | area |

#### 8.5.12 mmu\_enable

| trap#     | FAST_TRAP     |

|-----------|---------------|

| function# | MMU_ENABLE    |

| arg0      | enable_flag   |

| arg1      | return_target |

| ret0      | status        |

This function either enables or disables virtual address translation for the calling CPU within the virtual machine domain. If the *enable\_flag* is zero, translation is disabled, any non-zero value will enable translation.

When this function returns, the newly selected translation mode will be active. The argument *return\_target* is a virtual address if translation is being enabled, or *return\_target* is a real address in the event that translation is to be disabled.

Upon successful completion, this API service will return control to the *return\_target* address with the new operating mode. In the event of call failure, the previous operating mode remains, and the service simply returns to the caller with the appropriate error code in ret0.

#### 8.5.12.1 Errors

| ENORADDR  | Invalid real address when disabling translation |

|-----------|-------------------------------------------------|

| EBADALIGN | return_target is not aligned to an instruction  |

| EINVAL    | enable_flag requests current operating mode;    |

|           | (e.g. disable if already disabled).             |

## 8.5.13 mmu\_tsb\_ctx0\_info

| trap#     | FAST_TRAP         |

|-----------|-------------------|

| function# | MMU_TSB_CTX0_INFO |

| arg0      | maxtsbs           |

| arg1      | bufferptr         |

| ret0      | status            |

| ret1      | ntsbs             |

This function returns the TSB configuration as previously defined by **mmu\_tsb\_ctx0** into the buffer provided by arg1. The size of the buffer is given in arg1 in terms of number of TSB description entries.

Upon return, ret1 <u>always</u> contains the number of TSB descriptions previously <u>configured</u> contains the number of TSB descriptions previously configured. If the supplied buffer was too small, then EINVAL is returned in ret0, otherwise EOK is returned and ret1 TSB descriptions have been copied into the buffer. If zero TSBs were configured, then EOK is returned with ret1 containing 0.

If zero TSBs were configured, then EOK is returned with ret1 containing 0.

## 8.5.13.1 <u>Errors</u>

| EINVAL    | <u>supplied buffer (maxtsbs) is too small</u>    |

|-----------|--------------------------------------------------|

| EBADALIGN | bufferptr is badly aligned                       |

| ENORADDR  | invalid real address for for buffer at bufferptr |

#### 8.5.14 mmu\_tsb\_ctxnon0\_info

| trap#     | FAST_TRAP            |

|-----------|----------------------|

| function# | MMU_TSB_CTXNON0_INFO |

| arg0      | maxtsbs              |

| arg1      | bufferptr            |

| ret0      | status               |

| ret1      | ntsbs                |

This function returns the TSB configuration as previously defined by **mmu\_tsb\_ctxnon0** into the buffer provided by arg1. The size of the buffer is given in arg1 in terms of number of TSB description entries.

Upon return ret1 always contains the number of TSB descriptions previously configured., ret1 contains the number of TSB descriptions previously configured. If the supplied buffer was too small, then EINVAL is returned in ret0, otherwise EOK is returned and ret1 TSB descriptions have been copied into the buffer. If zero TSBs were configured, then EOK is returned with ret1 containing 0.

If zero TSBs were configured, then EOK is returned with ret1 containing 0.

### 8.5.14.1 <u>Errors</u>

| EINVAL    | <u>supplied buffer (maxtsbs) is too small</u>    |

|-----------|--------------------------------------------------|

| EBADALIGN | bufferptr is badly aligned                       |

| ENORADDR  | invalid real address for for buffer at bufferptr |

### 8.5.15 mmu fault area info

| <u>trap#</u> | FAST TRAP           |

|--------------|---------------------|

| function#    | MMU FAULT AREA INFO |

|              |                     |

| <u>ret0</u>  | status              |

| <u>ret1</u>  | <u>fara</u>         |

|              |                     |

<u>This API service returns the currently defined MMU fault status area for the current</u> <u>CPU. The real address of the fault status area is returned in ret1, or 0 is returned in ret1 if no</u> <u>fault status area is defined.</u>

Note: mmu\_fault\_area\_conf may be called with the return value (ret1) from this service if there is a need to save and restore the fault area for a cpu.

8.5.15.1 Errors

no errors are defined EINVAL Invalid buffer size

## 9 Cache and Memory services

In general, caches and memory are not exposed to the supervisor, although they are described to it in the machine description.

## 9.1 API calls

## 9.1.1 mem\_scrub

| trap#     | FAST_TRAP       |

|-----------|-----------------|

| function# | MEM_SCRUB       |

| arg0      | raddr           |

| arg1      | length          |

| ret0      | status          |

| ret1      | length scrubbed |

This service zeros the memory contents for the memory address range raddr to raddr+length<u>-1</u>. It also creates a valid error-checking code for the memory address range raddr to raddr+length-1.

This service starts scrubbing at raddr, but may scrub less than length bytes of memory. On success the actual length scrubbed is returned in ret1.

The arguments raddr and length must be aligned to an 8K page boundary or must contain the start address and length from a sun4v error report.

Note: There are two uses for this function: The first use is to block clear and initialize memory and the second is to scrub an uncorrectable error reported via a resumable or non-resumable trap. The second use requires the arguments to be equal to the raddr and length provided in a sun4v memory error report.

9.1.1.1 Errors

| ENORADDR  | Invalid <i>raddr</i>                   |

|-----------|----------------------------------------|

| EBADALIGN | Either the start address or length are |

|           | not correctly aligned.                 |

| EINVAL    | length == 0                            |

| trap#     | FAST_TRAP     |

|-----------|---------------|

| function# | MEM_SYNC      |

| arg0      | raddr         |

| arg1      | length        |

| ret0      | status        |

| ret1      | length synced |

For the memory address range *raddr* to *raddr*+*length*-1, this service forces the next access within that range to be fetched from main system memory.

This service starts syncing at *raddr*, but may sync less than *length* bytes of memory. On success the actual length synced is returned in ret1.

The arguments *raddr* and *length* must be aligned to an 8K page boundary.

9.1.2.1 Errors

| ENORADDR  | Invalid <i>raddr</i>                   |

|-----------|----------------------------------------|

| EBADALIGN | Either the start address or length are |

|           | not correctly aligned.                 |

| EINVAL    | length == 0                            |

Hypervisor API

## 10 Device interrupt services

Device interrupts are allocated to system bus bridges by the hypervisor, and described to the boot firmware in the machine description. OBP then describes them to Solaris via the device tree. The services described here are the generic interrupt services only, it is expected that the system bus nexus drivers will have additional APIs for functions that are specific to that bridge.

## 10.1 Definitions

These definitions apply to the following services:

| cpuid            | A unique opaque value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | which repre   | sents a target cpu.                                                                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------|