# UltraSPARC Virtual Machine Specification

## **UltraSPARC Virtual Machine Specification**

Compiled from hg version 3033604f0239 3.0-draft7

#### Publication date 2012-03-13 19:43

Copyright © 2008, 2010 Oracle and/or its affiliates. All rights reserved. Copyright © 2008, 2010 Oracle et/ou ses ailiés. Tous droits réservés.

This software and related documentation are provided under a license agreement containing restrictions on use and disclosure and are protected by intellectual property laws. Except as expressly permitted in your license agreement or allowed by law, you may not use, copy, reproduce, translate, broadcast, modify, license, transmit, distribute, exhibit, perform, publish, or display any part, in any form, or by any means. Reverse engineering, disassembly, or decompilation of this software, unless required by law for interoperability, is prohibited.

The information contained herein is subject to change without notice and is not warranted to be error-free. If you find any errors, please report them to us in writing.

If this is software or related software documentation that is delivered to the U.S. Government or anyone licensing it on behalf of the U.S. Government, the following notice is applicable:

U.S. GOVERNMENT RIGHTS Programs, software, databases, and related documentation and technical data delivered to U.S. Government customers are "commercial computer software" or "commercial technical data" pursuant to the applicable Federal Acquisition Regulation and agency-specific supplemental regulations. As such, the use, duplication, disclosure, modification, and adaptation shall be subject to the restrictions and license terms set forth in the applicable Government contract, and, to the extent applicable by the terms of the Government contract, the additional rights set forth in FAR 52.227-19, Commercial Computer Software License (December 2007). Oracle America, Inc., 500 Oracle Parkway, Redwood City, CA 94065.

This software or hardware is developed for general use in a variety of information management applications. It is not developed or intended for use in any inherently dangerous applications, including applications which may create a risk of personal injury. If you use this software or hardware in dangerous applications, then you shall be responsible to take all appropriate fail-safe, backup, redundancy, and other measures to ensure its safe use. Oracle Corporation and its affiliates disclaim any liability for any damages caused by use of this software or hardware in dangerous applications.

Oracle and Java are registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners.

AMD, Opteron, the AMD logo, and the AMD Opteron logo are trademarks or registered trademarks of Advanced Micro Devices. Intel and Intel Xeon are trademarks or registered trademarks of Intel Corporation. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. UNIX is a registered trademark licensed through X/Open Company, Ltd.

This software or hardware and documentation may provide access to or information on content, products, and services from third parties. Oracle Corporation and its affiliates are not responsible for and expressly disclaim all warranties of any kind with respect to third-party content, products, and services. Oracle Corporation and its affiliates will not be responsible for any loss, costs, or damages incurred due to your access to or use of third-party content, products, or services.

Ce logiciel et la documentation qui l'accompagne sont protégés par les lois sur la propriété intellectuelle. Ils sont concédés sous licence et soumis à des restrictions d'utilisation et de divulgation. Sauf disposition de votre contrat de licence ou de la loi, vous ne pouvez pas copier, reproduire, traduire, diffuser, modifier, breveter, transmettre, distribuer, exposer, exécuter, publier ou afficher le logiciel, même partiellement, sous quelque forme et par quelque procédé que ce soit. Par ailleurs, il est interdit de procéder à toute ingénierie inverse du logiciel, de le désassembler ou de le décompiler, excepté à des fins d'interopérabilité avec des logiciels tiers ou tel que prescrit par la loi.

Les informations fournies dans ce document sont susceptibles de modification sans préavis. Par ailleurs, Oracle Corporation ne garantit pas qu'elles soient exemptes d'erreurs et vous invite, le cas échéant, à lui en faire part par écrit.

Si ce logiciel, ou la documentation qui l'accompagne, est concédé sous licence au Gouvernement des Etats-Unis, ou à toute entité qui délivre la licence de ce logiciel ou l'utilise pour le compte du Gouvernement des Etats-Unis, la notice suivante s'applique:

U.S. GOVERNMENT RIGHTS. Programs, software, databases, and related documentation and technical data delivered to U.S. Government customers are "commercial computer software" or "commercial technical data" pursuant to the applicable Federal Acquisition Regulation and agency-specific supplemental regulations. As such, the use, duplication, disclosure, modification, and adaptation shall be subject to the restrictions and license terms set forth in the applicable Government contract, and, to the extent applicable by the terms of the Government contract, the additional rights set forth in FAR 52.227-19, Commercial Computer Software License (December 2007). Oracle America, Inc., 500 Oracle Parkway, Redwood City, CA 94065.

Ce logiciel ou matériel a été développé pour un usage général dans le cadre d'applications de gestion des informations. Ce logiciel ou matériel n'est pas conçu ni n'est destiné à être utilisé dans des applications à risque, notamment dans des applications pouvant causer des dommages corporels. Si vous utilisez ce logiciel ou matériel dans le cadre d'applications dangereuses, il est de votre responsabilité de prendre toutes les mesures de secours, de sauvegarde, de redondance et autres mesures nécessaires à son utilisation dans des conditions optimales de sécurité. Oracle Corporation et ses affiliés déclinent toute responsabilité quant aux dommages causés par l'utilisation de ce logiciel ou matériel pour ce type d'applications.

Oracle et Java sont des marques déposées d'Oracle Corporation et/ou de ses affiliés. Tout autre nom mentionné peut correspondre à des marques appartenant à d'autres propriétaires qu'Oracle.

AMD, Opteron, le logo AMD et le logo AMD Opteron sont des marques ou des marques déposées d'Advanced Micro Devices. Intel et Intel Xeon sont des marques ou des marques déposées d'Intel Corporation. Toutes les marques SPARC sont utilisées sous licence et sont des marques ou des marques déposées de SPARC International, Inc. UNIX est une marque déposée concédé sous license par X/Open Company, Ltd.

## **Table of Contents**

| Preface                                        | xvii |

|------------------------------------------------|------|

| 1. Foreward                                    | xvii |

| 2. Related specifications                      | xvii |

| 1. Overview                                    | 1    |

| 1.1. Architectural requirements                | 1    |

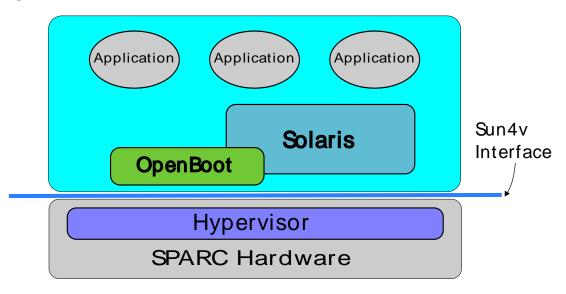

| 1.2. The hypervisor and sun4v architecture     |      |

| 1.3. Privilege, isolation and virtualization   | 2    |

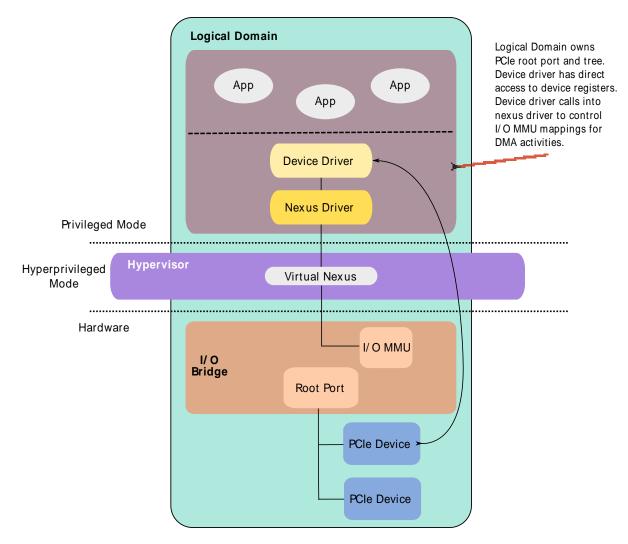

| 1.4. Direct I/O                                | 3    |

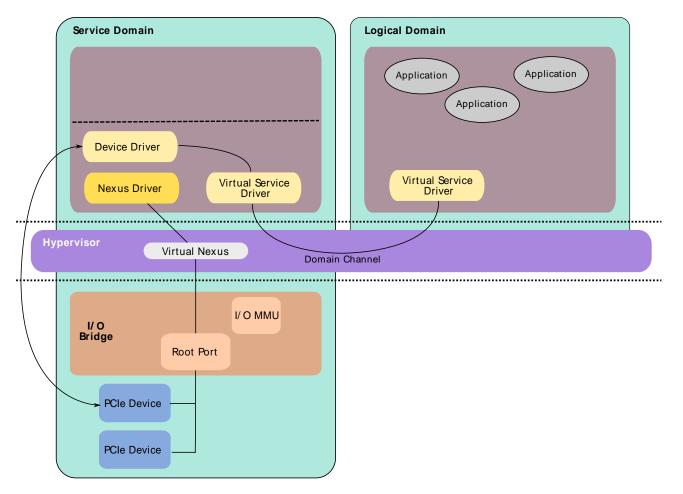

| 1.5. Logical Domain Channels                   | 5    |

| 1.5.1. Stateless connections                   | 6    |

| 1.5.2. LDC security                            | 6    |

| 1.6. Machine Descriptions                      | 6    |

| 1.7. Virtual I/O                               |      |

| 1.7.1. Abstraction                             | 9    |

| 1.7.2. Stateless connections & multipathed I/O | 9    |

| 1.7.3. Virtual disk services                   |      |

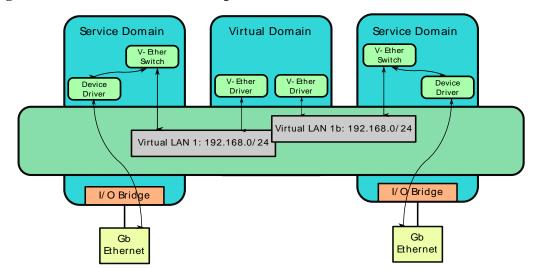

| 1.7.4. Scalable virtual networking services    |      |

| 1.7.5. Virtual I/O Limits                      |      |

| 1.8. Hybrid I/O                                |      |

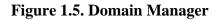

| 1.9. Logical Domain Manager                    |      |

| 1.9.1. Domain roles                            |      |

| 1.9.2. Domain dependencies                     |      |

| 1.9.3. Domain manager operation                |      |

| 1.10. Domain service infrastructure            |      |

| 1.11. OpenBoot firmware                        |      |

| 1.12. Error Handling                           |      |

| 1.13. Advanced LDoms features                  |      |

| 1.13.1. Dynamic reconfiguration                |      |

| 1.13.2. Logical domain migration               |      |

| 2. Hypervisor call conventions                 |      |

|                                                |      |

| 2.1. Hyper-fast traps                          |      |

| 2.2. Fast traps                                |      |

| 2.3. Post hypervisor trap processing           |      |

| 3. State Definitions                           |      |

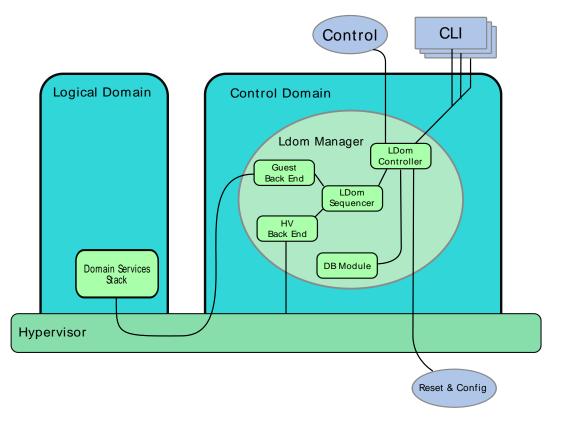

| 3.1. Processor states                          |      |

| 3.2. Initial guest environment                 |      |

| 3.3. Privileged registers                      |      |

| 3.3.1. Non-Privileged Registers                |      |

| 3.3.2. Ancillary State Registers               |      |

| 3.3.3. Internal memory-mapped registers        |      |

| 3.3.4. CPU-specific Registers                  |      |

| 3.4. Other initial guest state                 |      |

| 4. Addressing Models                           |      |

| 4.1. Background                                |      |

| 4.2. Address types                             |      |

| 4.3. Address spaces                            |      |

| 4.4. Address space identifiers                 |      |

| 4.4.1. ASI 0x14 & 0x1c: REAL_MEM{_LITTLE}      |      |

| 4.4.2. ASI 0x15 & 0x1d: REAL_IO{_LITTLE}       |      |

| 4.4.3. ASI 0x26 & 0x2E: REAL_QUAD{_LITTLE}     |      |

| 4.4.4. ASI 0x21: MMU                           | . 26 |

|                                                                                                                                                                                                                                                                                                                                       | 07                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 4.5. Translation mappings                                                                                                                                                                                                                                                                                                             |                                              |

| 4.6. MMU Demap support                                                                                                                                                                                                                                                                                                                |                                              |

| 4.7. MMU traps                                                                                                                                                                                                                                                                                                                        |                                              |

| 4.8. MMU fault status area                                                                                                                                                                                                                                                                                                            |                                              |

| 5. Trap Model                                                                                                                                                                                                                                                                                                                         |                                              |

| 5.1. Privilege mode trap processing                                                                                                                                                                                                                                                                                                   | 29                                           |

| 5.2. Trap levels                                                                                                                                                                                                                                                                                                                      | 29                                           |

| 5.2.1. Privilege mode TL overflow                                                                                                                                                                                                                                                                                                     | 29                                           |

| 5.3. Sun4v privileged-mode trap table                                                                                                                                                                                                                                                                                                 | 29                                           |

| 6. Interrupt model                                                                                                                                                                                                                                                                                                                    |                                              |

| 6.1. Definitions                                                                                                                                                                                                                                                                                                                      |                                              |

| 6.2. Interrupt reports                                                                                                                                                                                                                                                                                                                |                                              |

| 6.3. Interrupt queues                                                                                                                                                                                                                                                                                                                 |                                              |

| 6.3.1. Queue support registers                                                                                                                                                                                                                                                                                                        |                                              |

|                                                                                                                                                                                                                                                                                                                                       |                                              |

| 6.4. Interrupt traps                                                                                                                                                                                                                                                                                                                  |                                              |

| 6.4.1. CPU mondo interrupts                                                                                                                                                                                                                                                                                                           |                                              |

| 6.4.2. Device mondo interrupts                                                                                                                                                                                                                                                                                                        |                                              |

| 6.5. Device interrupts                                                                                                                                                                                                                                                                                                                |                                              |

| 6.5.1. Device handles and devinos                                                                                                                                                                                                                                                                                                     | 32                                           |

| 6.6. Sysinos and cookies                                                                                                                                                                                                                                                                                                              | 32                                           |

| 6.6.1. Legacy use (the sysino)                                                                                                                                                                                                                                                                                                        | 32                                           |

| 6.6.2. Interrupt cookies                                                                                                                                                                                                                                                                                                              |                                              |

| 7. Error model                                                                                                                                                                                                                                                                                                                        |                                              |

| 7.1. Definitions                                                                                                                                                                                                                                                                                                                      |                                              |

| 7.2. 7.2 Error classes                                                                                                                                                                                                                                                                                                                |                                              |

| 7.2. 7.2 Enfor classes                                                                                                                                                                                                                                                                                                                |                                              |

|                                                                                                                                                                                                                                                                                                                                       |                                              |

| 7.2.2. Non-resumable error                                                                                                                                                                                                                                                                                                            |                                              |

| 7.3. Error reports                                                                                                                                                                                                                                                                                                                    |                                              |

| 7.4. Error queues                                                                                                                                                                                                                                                                                                                     |                                              |

| 7.4.1. Error Queue Head and Tail Pointers                                                                                                                                                                                                                                                                                             |                                              |

| 7.5. Error traps                                                                                                                                                                                                                                                                                                                      |                                              |

| 8. Machine description                                                                                                                                                                                                                                                                                                                | 37                                           |

| 8.1. Requirements                                                                                                                                                                                                                                                                                                                     | 37                                           |

| 8.2. Sections                                                                                                                                                                                                                                                                                                                         | 37                                           |

| 8.3. Encoding                                                                                                                                                                                                                                                                                                                         | 37                                           |

| 8.4. Header                                                                                                                                                                                                                                                                                                                           |                                              |

| 8.4.1. Version numbering                                                                                                                                                                                                                                                                                                              |                                              |

| 8.4.2. Size fields                                                                                                                                                                                                                                                                                                                    |                                              |

| 8.5. Name Block                                                                                                                                                                                                                                                                                                                       |                                              |

| 8.6. Data Block                                                                                                                                                                                                                                                                                                                       |                                              |

|                                                                                                                                                                                                                                                                                                                                       |                                              |

| 8.7. Node Block                                                                                                                                                                                                                                                                                                                       |                                              |

| 8.7.1. Element format                                                                                                                                                                                                                                                                                                                 |                                              |

| 8.7.2. Tag definitions                                                                                                                                                                                                                                                                                                                |                                              |

|                                                                                                                                                                                                                                                                                                                                       | 41                                           |

| 8.8. Nodes                                                                                                                                                                                                                                                                                                                            |                                              |

| 8.8. Nodes         8.9. Node definitions                                                                                                                                                                                                                                                                                              |                                              |

| <ul> <li>8.8. Nodes</li></ul>                                                                                                                                                                                                                                                                                                         | 42                                           |

| <ul> <li>8.8. Nodes</li></ul>                                                                                                                                                                                                                                                                                                         | 42<br>42                                     |

| <ul> <li>8.8. Nodes</li></ul>                                                                                                                                                                                                                                                                                                         | 42<br>42                                     |

| <ul> <li>8.8. Nodes</li></ul>                                                                                                                                                                                                                                                                                                         | 42<br>42<br>43                               |

| <ul> <li>8.8. Nodes</li></ul>                                                                                                                                                                                                                                                                                                         | 42<br>42<br>43<br>43                         |

| <ul> <li>8.8. Nodes</li> <li>8.9. Node definitions</li> <li>8.9.1. Node categories</li> <li>8.10. Content versions</li> <li>8.11. Common data definitions</li> <li>8.11.1. String array</li> <li>8.12. How to use a machine description</li> </ul>                                                                                    | 42<br>42<br>43<br>43<br>43                   |

| <ul> <li>8.8. Nodes</li> <li>8.9. Node definitions</li> <li>8.9.1. Node categories</li> <li>8.10. Content versions</li> <li>8.11. Common data definitions</li> <li>8.11.1. String array</li> <li>8.12. How to use a machine description</li> <li>8.12.1. Using the MD as a list</li> </ul>                                            | 42<br>42<br>43<br>43<br>43<br>43             |

| <ul> <li>8.8. Nodes</li> <li>8.9. Node definitions</li> <li>8.9.1. Node categories</li> <li>8.10. Content versions</li> <li>8.11. Common data definitions</li> <li>8.11.1. String array</li> <li>8.12. How to use a machine description</li> <li>8.12.1. Using the MD as a list</li> <li>8.13. Accelerating string lookups</li> </ul> | 42<br>42<br>43<br>43<br>43<br>43<br>43<br>44 |

| <ul> <li>8.8. Nodes</li> <li>8.9. Node definitions</li> <li>8.9.1. Node categories</li> <li>8.10. Content versions</li> <li>8.11. Common data definitions</li> <li>8.11.1. String array</li> <li>8.12. How to use a machine description</li> <li>8.12.1. Using the MD as a list</li> </ul>                                            | 42<br>42<br>43<br>43<br>43<br>43<br>44<br>45 |

| 8.15. DAG construction                                                    |        |

|---------------------------------------------------------------------------|--------|

| 8.16. Required nodes                                                      | <br>46 |

| 8.17. The vanilla MD                                                      |        |

| 8.18. Formation and meaning of a DAG                                      | <br>46 |

| 8.19. Generic nodes                                                       |        |

| 8.19.1. Root node                                                         | <br>47 |

| 8.19.2. Cpus node                                                         | <br>47 |

| 8.19.3. cpu node                                                          | <br>48 |

| 8.19.4. Memory node                                                       | <br>50 |

| 8.19.5. Mblock node                                                       | <br>51 |

| 8.19.6. Platform node                                                     | <br>51 |

| 8.19.7. Domain services node                                              | <br>54 |

| 8.19.8. Domain services port node                                         | <br>54 |

| 8.20. Memory hierarchy nodes                                              | <br>54 |

| 8.20.1. Cache node                                                        | <br>54 |

| 8.20.2. Exec-unit node                                                    | <br>55 |

| 8.20.3. TLB node                                                          |        |

| 8.21. Variables                                                           |        |

| 8.21.1. Description                                                       |        |

| 8.22. Keystore                                                            |        |

| 8.22.1. Description                                                       |        |

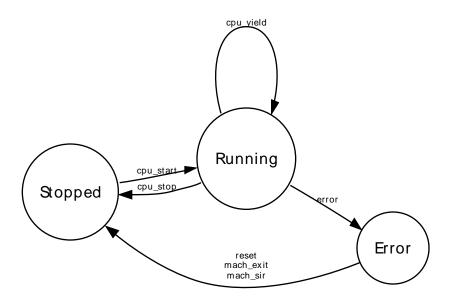

| 8.23. Virtual Devices                                                     |        |

| 8.23.1. Descriptions for virtual devices                                  |        |

| 8.23.2. Virtual devices node                                              |        |

| 8.23.3. Channel devices node                                              |        |

| 8.23.4. Virtual device node                                               |        |

| 8.23.5. Virtual device port node                                          |        |

| 8.23.6. Channel endpoints node                                            |        |

| 8.23.7. Description                                                       |        |

| 8.23.8. Channel endpoint node                                             |        |

| 8.23.9. RNG virtual-device node                                           |        |

| 8.23.10. Crypto virtual-device node                                       |        |

| 8.23.11. MAC-addresses node                                               |        |

| 8.23.12. MAC-address node                                                 |        |

|                                                                           |        |

| 8.24. Latency nodes                                                       |        |

| 8.24.1. Programming notes and accuracy                                    |        |

| 8.24.2. Memory latency group node<br>8.24.3. Programmed I/O latency group |        |

|                                                                           |        |

| 8.24.4. I/O DMA latency group                                             |        |

| 8.24.5. I/O Interrupt latency group node                                  |        |

| 8.24.6. Latency groups node                                               |        |

| 8.25. I/O device nodes                                                    |        |

| 8.25.1. Physical Device Collection node                                   |        |

| 8.25.2. I/O device node                                                   |        |

| 8.25.3. UltraSPARC-T2 NIU network device node                             |        |

| 8.25.4. Interrupt mapping node                                            |        |

| 8.25.5. Slot name node                                                    |        |

| 8.25.6. Device name alias node                                            |        |

| 8.25.7. I/O device path aliases collection node                           |        |

| 8.25.8. I/O device path alias node                                        |        |

| 9. Logical domain variables                                               |        |

| 9.1. Overview                                                             |        |

| 9.2. LDom variable store                                                  |        |

| 9.3. LDom variables and automatic reboot                                  | <br>84 |

| 9.3.1. Format of reboot-command variable             | 85   |

|------------------------------------------------------|------|

| 9.3.2. Guest OS management of LDom variables         |      |

| 10. Security keys                                    |      |

| 11. API versioning                                   |      |

| 11.1. API calls                                      |      |

| 11.1.1. api_set_version                              |      |

| •                                                    |      |

| 11.1.2. api_get_version                              |      |

| 12. Core services                                    |      |

| 12.1. API calls                                      |      |

| 12.1.1. mach_exit                                    |      |

| 12.1.2. mach_desc                                    |      |

| 12.1.3. mach_sir                                     |      |

| 12.1.4. mach_set_watchdog                            |      |

| 12.1.5. mach_suspend                                 |      |

| 12.1.6. mach_pri                                     |      |

| 12.1.7. mach_vars                                    | . 94 |

| 12.1.8. mach_reboot_data_set                         | . 95 |

| 12.1.9. mach_reboot_data_get                         | . 96 |

| 13. CPU services                                     | . 98 |

| 13.1. CPU id and CPU list                            | . 98 |

| 13.2. API calls                                      | . 98 |

| 13.2.1. cpu_start                                    | . 98 |

| 13.2.2. cpu_stop                                     |      |

| 13.2.3. cpu_set_rtba                                 |      |

| 13.2.4. cpu_get_rtba                                 |      |

| 13.2.5. cpu_yield                                    |      |

| 13.2.6. cpu_qconf                                    |      |

| 13.2.7. cpu_qinfo                                    |      |

| 13.2.8. cpu_mondo_send                               |      |

| •                                                    |      |

| 13.2.9. cpu_myid                                     |      |

| 13.2.10. cpu_state                                   |      |

| 13.2.11. cpu_tick_npt                                |      |

| 13.2.12. cpu_stick_npt                               |      |

| 14. MMU services                                     |      |

| 14.1. Translation Storage Buffer (TSB) specification |      |

| 14.1.1. Page sizes                                   |      |

| 14.1.2. Context index                                |      |

| 14.2. MMU flags                                      |      |

| 14.3. Translation table entries                      | 106  |

| 14.3.1. TSB entry tag word                           | 106  |

| 14.3.2. TSB entry data word                          | 107  |

| 14.4. Translation storage buffer (TSB) configuration | 108  |

| 14.5. Permanent and non-permanent mappings           | 108  |

| 14.6. MMU Fault status area                          | 108  |

| 14.7. Global MMU Operations                          |      |

| 14.8. API calls                                      |      |

| 14.8.1. mmu_tsb_ctx0                                 |      |

| 14.8.2. mmu_tsb_ctxnon0                              |      |

| 14.8.3. mmu_demap_page                               |      |

| 14.8.4. mmu_demap_ctx                                |      |

| 14.8.5. mmu_demap_ctx                                |      |

| 14.8.6. mmu_map_addr                                 |      |

| •                                                    |      |

| 14.8.7. mmu_map_perm_addr                            |      |

| 14.8.8. mmu_unmap_addr                               | 115  |

| 14.8.9. mmu_unmap_perm_addr               |     |

|-------------------------------------------|-----|

| 14.8.10. mmu_fault_area_conf              |     |

| 14.8.11. mmu_enable                       |     |

| 14.8.12. mmu_tsb_ctx0_info                |     |

| 14.8.13. mmu_tsb_ctxnon0_info             |     |

| 14.8.14. mmu_fault_area_info              | 118 |

| 14.8.15. mmu_global_demap_page            | 118 |

| 14.8.16. mmu_global_demap_ctx             | 119 |

| 14.8.17. mmu_global_demap_all             | 119 |

| 14.8.18. mmu_global_demap_status          | 120 |

| 15. Cache and Memory services             | 121 |

| 15.1. API calls                           | 121 |

| 15.1.1. mem_scrub                         | 121 |

| 15.1.2. mem_sync                          |     |

| 16. Device interrupt services             |     |

| 16.1. Definitions                         |     |

| 16.2. API calls                           |     |

| 16.2.1. vintr_getcookie                   |     |

| 16.2.2. vintr_setcookie                   |     |

| 16.2.3. vintr_getenabled                  |     |

|                                           |     |

| 16.2.4. vintr_setenabled                  |     |

| 16.2.5. vintr_getstate                    |     |

| 16.2.6. vintr_setstate                    |     |

| 16.2.7. vintr_gettarget                   |     |

| 16.2.8. vintr_settarget                   |     |

| 16.3. Deprecated API calls                |     |

| 16.3.1. intr_devino_to_sysino             |     |

| 16.3.2. intr_getenabled                   |     |

| 16.3.3. intr_setenabled                   | 127 |

| 16.3.4. intr_getstate                     | 128 |

| 16.3.5. intr_setstate                     | 128 |

| 16.3.6. intr_gettarget                    | 128 |

| 16.3.7. intr_settarget                    | 129 |

| 16.4. Interrupt API version control       | 129 |

| 17. Time of day services                  | 131 |

| 17.1. API calls                           |     |

| 17.1.1. tod_get                           | 131 |

| · · · · · · · · · · · · · · · · · · ·     | 131 |

|                                           | 132 |

| 18.1. API calls                           | -   |

|                                           | 132 |

|                                           | 132 |

| -                                         | 132 |

|                                           | 132 |

|                                           |     |

| 19. Domain state services                 |     |

| 19.1. API calls                           |     |

| 19.1.1. soft_state_set                    |     |

| = -8                                      | 136 |

| 20. Core dump services                    |     |

| 20.1. API calls                           |     |

| 20.1.1. dump_buf_update                   | 138 |

| · · · · · · · · · · · · · · · · · · ·     | 139 |

| 21. Trap trace services                   | 140 |

| 21.1. Trap trace buffer control structure | 140 |

|                                             | 1.10 |

|---------------------------------------------|------|

| 21.2. Trap trace buffer entry format        |      |

| 21.3. API calls                             |      |

| 21.3.1. ttrace_buf_conf                     |      |

| 21.3.2. ttrace_buf_info                     |      |

| 21.3.3. ttrace_enable                       |      |

| 21.3.4. ttrace_freeze                       |      |

| 21.3.5. ttrace_addentry                     |      |

| 22. Logical Domain Channel services         |      |

| 22.1. Endpoints                             | 144  |

| 22.2. LDC queues                            |      |

| 22.3. LDC interrupts                        |      |

| 22.4. API calls                             | 145  |

| 22.4.1. ldc_tx_qconf                        | 145  |

| 22.4.2. ldc_tx_qinfo                        | 146  |

| 22.4.3. ldc_tx_get_state                    | 146  |

| 22.4.4. ldc_tx_set_qtail                    | 147  |

| 22.4.5. ldc_rx_qconf                        | 147  |

| 22.4.6. ldc_rx_qinfo                        |      |

| 22.4.7. ldc_rx_get_state                    |      |

| 22.4.8. ldc_rx_set_qhead                    |      |

| 22.5. Shared Memory API calls               |      |

| 22.5.1. ldc_set_map_table                   |      |

| 22.5.1. ldc_get_map_table                   |      |

| 22.5.3. ldc_copy                            |      |

| 22.5.5. ldc_copy                            |      |

| 22.5.5. ldc_unmap                           |      |

| 22.5.5. ldc_revoke                          |      |

| 23. PCI I/O Services                        |      |

|                                             |      |

| 23.1. Introduction                          |      |

| 23.1.1. External documents                  |      |

| 23.2. IO Data Definitions                   |      |

| 23.3. PCI IO Data Definitions               |      |

| 23.4. API calls                             |      |

| 23.4.1. pci_iommu_map                       |      |

| 23.4.2. pci_iommu_demap                     |      |

| 23.4.3. pci_iommu_getmap                    |      |

| 23.4.4. pci_iommu_getbypass                 |      |

| 23.4.5. pci_config_get                      |      |

| 23.4.6. pci_config_put                      | 160  |

| 23.4.7. pci_peek                            | 161  |

| 23.4.8. pci_poke                            | 161  |

| 23.4.9. pci_dma_sync                        | 162  |

| 23.5. Static Direct I/O                     | 163  |

| 23.5.1. SDIO Definitions                    |      |

| 23.5.2. SDIO API Definitions                |      |

| 24. PCI MSI Services                        |      |

| 24.1. Message Signaled Interrupt (MSI)      |      |

| 24.2. MSI Event Queue (MSI EQ)              |      |

| 24.2.1. MSI/Message/INTx Data Record format |      |

|                                             | 169  |

| 24.3. Definitions                           |      |

| 24.4.1. pci_msiq_conf                       |      |

| 24.4.1. pci_nisiq_coni                      |      |

|                                             |      |

| 24.4.3. pci_msiq_getvalid                   | 1/1  |

| 24.4.4. pci_msiq_setvalid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 24.4.5. pci_msiq_getstate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 24.4.6. pci_msiq_setstate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 24.4.7. pci_msiq_gethead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 24.4.8. pci_msiq_sethead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 24.4.9. pci_msiq_gettail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 24.4.10. pci_msi_getvalid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 174 |

| 24.4.11. pci_msi_setvalid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 174 |

| 24.4.12. pci_msi_getmsiq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 174 |

| 24.4.13. pci_msi_setmsiq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 175 |

| 24.4.14. pci_msi_getstate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 175 |

| 24.4.15. pci_msi_setstate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 175 |

| 24.4.16. pci_msg_getmsiq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 176 |